# ±300°/sec Yaw Rate Gyroscope with SPI

# ADIS16100

#### **FEATURES**

Complete angular rate gyroscope Z-axis (yaw rate) response SPI digital output interface High vibration rejection over wide frequency 2000 g-powered shock survivability Externally controlled self-test Internal temperature sensor output Dual auxiliary 12-bit ADC inputs Absolute rate output for precision applications 5 V single-supply operation 8.2 mm × 8.2 mm × 5.2 mm package RoHS compliant

#### APPLICATIONS

Platform stabilization Image stabilization Guidance and control Inertia measurement units Robotics

#### **GENERAL DESCRIPTION**

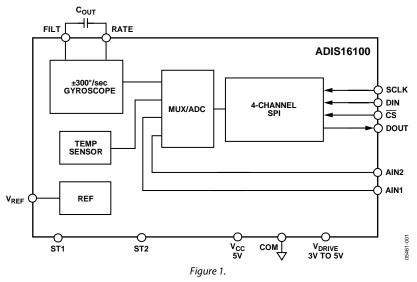

The ADIS16100 is a gyroscope that uses the Analog Devices, Inc. surface-micromachining process to make a functionally complete angular rate sensor with an integrated serial peripheral interface (SPI).

The digital data available at the SPI port is proportional to the angular rate about the axis that is normal to the top surface of the package (see Figure 20). A single external resistor can be used to increase the measurement range. An external capacitor can be used to lower the bandwidth.

Access to an internal temperature sensor measurement is provided through the SPI for compensation techniques. Two pins are available for the user to input analog signals for digitization. An additional output pin provides a precision voltage reference. Two digital self-test inputs electromechanically excite the sensor to test the operation of the sensor and the signal-conditioning circuits.

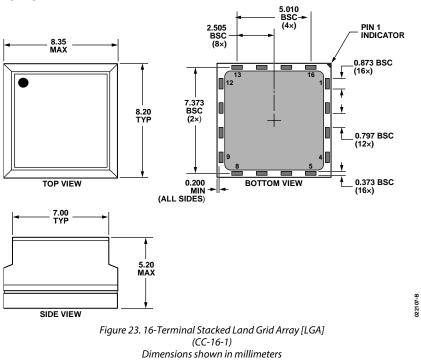

The ADIS16100 is available in an 8.2 mm  $\times$  8.2 mm  $\times$  5.2 mm, 16-terminal, peripheral land grid array (LGA) package.

#### FUNCTIONAL BLOCK DIAGRAM

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006-2007 Analog Devices, Inc. All rights reserved.

### TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| General Description 1                        |

| Functional Block Diagram 1                   |

| Revision History 2                           |

| Specifications                               |

| Timing Specifications 5                      |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

#### **REVISION HISTORY**

| 6/07—Rev. A to Rev. B                  |    |

|----------------------------------------|----|

| Changes to Table 1                     | 3  |

| Changes to Table 2                     | 5  |

| Changes to Absolute Maximum Ratings    | 6  |

| Changes to Table 4                     | 7  |

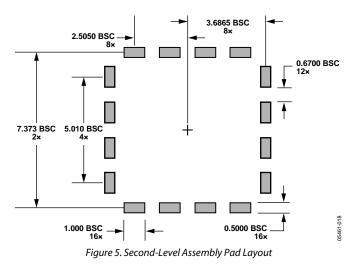

| Added Figure 5                         | 7  |

| Changes to Theory of Operation Section | 11 |

| Added Basic Operation Section          | 12 |

| Deleted Second Level Assembly Section  | 14 |

|                                        |    |

#### 5/06—Rev. 0 to Rev. A

| Changes to Table 1                   |  |

|--------------------------------------|--|

| Changes to Setting Bandwidth Section |  |

| Changes to Table 9 and Table 10      |  |

#### 1/06—Revision 0: Initial Version

| Theory of Operation 11              |

|-------------------------------------|

| Supply and Common Considerations 11 |

| Increasing Measurement Range 11     |

| Setting Bandwidth 11                |

| Self-Test Function 11               |

| Rate Sensitive Axis 11              |

| Basic Operation12                   |

| Serial Peripheral Interface (SPI)12 |

| Outline Dimensions                  |

| Ordering Guide14                    |

### **SPECIFICATIONS**

$T_A = 25^{\circ}C$ ,  $V_{CC} = V_{DRIVE} = 5$  V, angular rate = 0°/sec,  $C_{OUT} = 0 \ \mu$ F, ±1 g, unless otherwise noted.

#### Table 1.

| Parameter                                                             | Conditions                                                                         | Min <sup>1</sup>       | Тур    | Max <sup>1</sup>              | Unit       |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------|--------|-------------------------------|------------|

| SENSITIVITY                                                           |                                                                                    |                        |        |                               |            |

| Dynamic Range <sup>2</sup> Full-scale range over specifications range |                                                                                    | ±300                   |        |                               | °/sec      |

| Initial                                                               | Clockwise rotation is positive output,<br>$T_A = -40^{\circ}$ C to $+85^{\circ}$ C | 0.2212                 | 0.2439 | 0.2717                        | °/sec/LSB  |

| Change Over Temperature <sup>3</sup>                                  | $V_{CC} = V_{DRIVE} = 4.75 V \text{ to } 5.25 V$                                   |                        | ±5     |                               | %          |

| Nonlinearity                                                          | Best fit straight line                                                             |                        | 0.12   |                               | °/sec      |

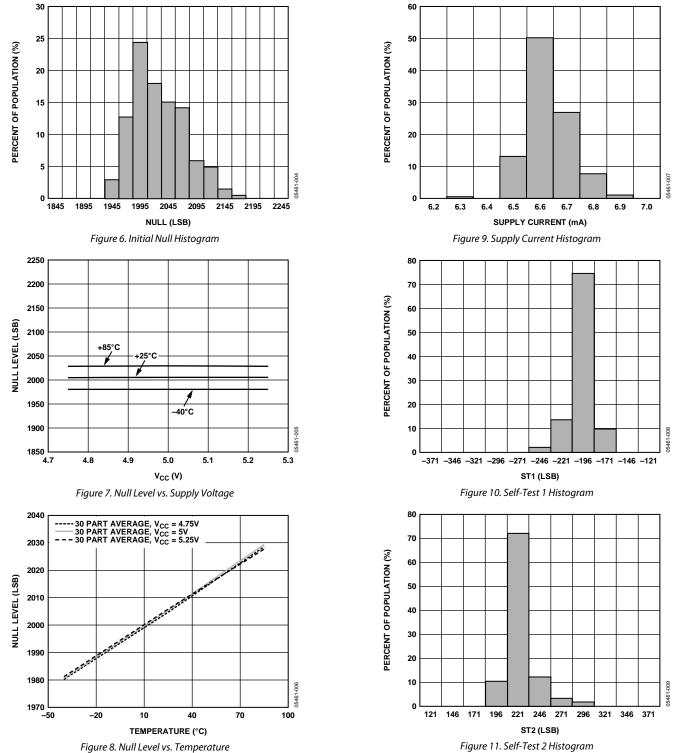

| NULL                                                                  |                                                                                    |                        |        |                               |            |

| Initial                                                               | Nominal 0°/sec output is 2048 LSB                                                  | -42                    |        | +37                           | °/sec      |

| Change Over Temperature <sup>3</sup>                                  | $V_{CC} = V_{DRIVE} = 4.75 V \text{ to } 5.25 V$                                   |                        | ±10    |                               | °/sec      |

| Turn-On Time                                                          | Power on to ±0.5°/sec of final value                                               |                        | 35     |                               | ms         |

| Linear Acceleration Effect                                            | Any axis                                                                           |                        | 0.2    |                               | °/sec/g    |

| Voltage Sensitivity                                                   | $V_{CC} = V_{DRIVE} = 4.75 V \text{ to } 5.25 V$                                   |                        | ±1     |                               | °/sec/V    |

| NOISE PERFORMANCE                                                     |                                                                                    |                        |        |                               |            |

| Total Noise                                                           | 0.1 Hz to 40 Hz; no averaging                                                      |                        | 0.43   |                               | °/sec rms  |

| Rate Noise Density                                                    | @ 25℃                                                                              |                        | 0.05   |                               | °/sec/√Hz  |

| FREQUENCY RESPONSE                                                    |                                                                                    |                        |        |                               |            |

| 3 dB Bandwidth (User-Selectable) <sup>4</sup>                         | $C_{OUT} = 0 \ \mu F$                                                              |                        | 40     |                               | Hz         |

| Sensor Resonant Frequency                                             |                                                                                    |                        | 14     |                               | kHz        |

| SELF-TEST INPUTS                                                      |                                                                                    |                        |        |                               |            |

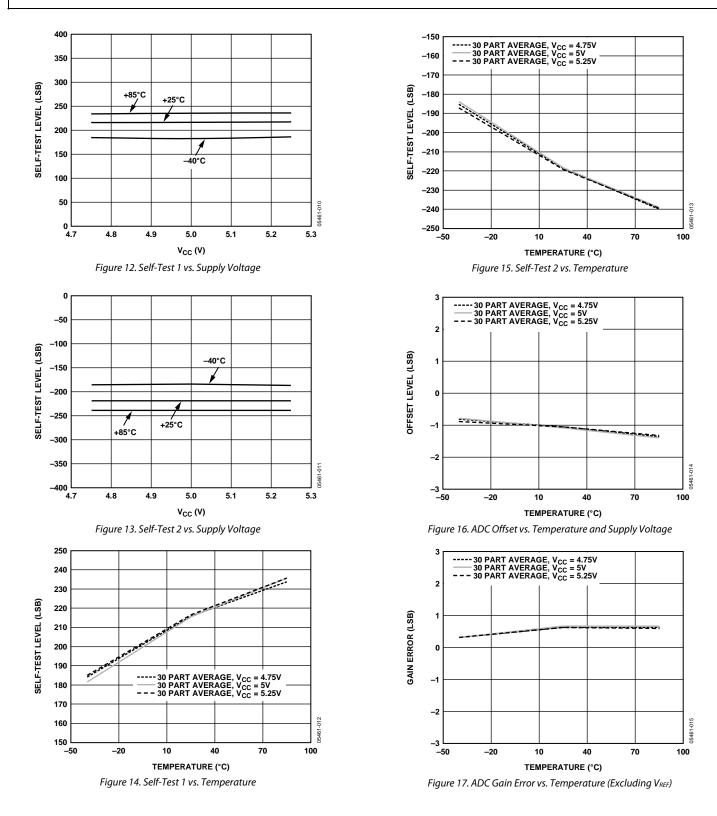

| ST1 Rateout Response⁵                                                 | ST1 pin from Logic 0 to Logic 1                                                    | -121                   | -221   | -376                          | LSB        |

| ST2 Rateout Response⁵                                                 | ST2 pin from Logic 0 to Logic 1                                                    | +121                   | +221   | +376                          | LSB        |

| Logic 1 Input Voltage                                                 | Standard high logic level definition                                               | 3.3                    |        |                               | V          |

| Logic 0 Input Voltage                                                 | Standard low logic level definition                                                |                        |        | 1.7                           | V          |

| Input Impedance                                                       | To common                                                                          |                        | 50     |                               | kΩ         |

| TEMPERATURE SENSOR                                                    |                                                                                    |                        |        |                               |            |

| Reading at 298 K                                                      |                                                                                    |                        | 2048   |                               | LSB        |

| Scale Factor                                                          | Proportional to absolute temperature                                               |                        | 0.1453 |                               | K/LSB      |

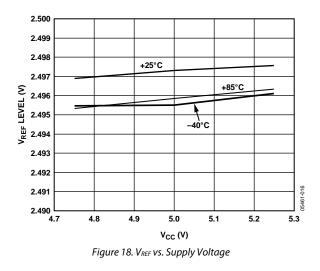

| 2.5 V REFERENCE                                                       |                                                                                    |                        |        |                               |            |

| Voltage Value                                                         |                                                                                    | 2.45                   | 2.5    | 2.55                          | v          |

| Load Drive to Ground                                                  | Source                                                                             |                        | 100    |                               | μA         |

| Load Regulation                                                       | 0 μΑ < Ι <sub>Ουτ</sub> < 100 μΑ                                                   |                        | 5.0    |                               | '<br>mV/mA |

| Power Supply Rejection                                                | $V_{CC} = V_{DRIVE} = 4.75 \text{ V} \text{ to } 5.25 \text{ V}$                   |                        | 1.0    |                               | mV/V       |

| Temperature Drift                                                     | Delta from 25°C                                                                    |                        | 5.0    |                               | mV         |

| LOGIC INPUTS                                                          |                                                                                    |                        |        |                               |            |

| Input High Voltage, VINH                                              |                                                                                    | $0.7 \times V_{DRIVE}$ |        |                               | v          |

| Input Low Voltage, V <sub>INL</sub>                                   |                                                                                    |                        |        | $0.3 \times V_{\text{DRIVE}}$ | V          |

| Input Current, I <sub>IN</sub>                                        | Typically 10 nA                                                                    | -1                     |        | +1                            | μA         |

| Input Capacitance, C <sub>IN</sub>                                    |                                                                                    |                        | 10     |                               | pF         |

| ANALOG INPUTS                                                         | For V <sub>IN</sub> < V <sub>CC</sub>                                              |                        |        |                               |            |

| Resolution                                                            |                                                                                    |                        | 12     |                               | Bits       |

| Integral Nonlinearity                                                 |                                                                                    | -2                     | -      | +2                            | LSB        |

| Differential Nonlinearity                                             |                                                                                    |                        |        | +2                            | LSB        |

| Offset Error                                                          |                                                                                    |                        |        | +8                            | LSB        |

| Gain Error                                                            |                                                                                    |                        |        | +2                            | LSB        |

| Input Voltage Range                                                   |                                                                                    |                        |        | $V_{REF} \times 2$            | V          |

| Leakage Current                                                       |                                                                                    |                        |        | +1                            | μA         |

| Input Capacitance                                                     |                                                                                    | -1                     | 20     |                               | pF         |

| Full Power Bandwidth                                                  |                                                                                    |                        | 8      |                               | MHz        |

| Parameter                                | Conditions                                                  | Min <sup>1</sup>        | Тур | Max <sup>1</sup> | Unit |

|------------------------------------------|-------------------------------------------------------------|-------------------------|-----|------------------|------|

| DIGITAL OUTPUTS                          |                                                             |                         |     |                  |      |

| Output High Voltage (V <sub>он</sub> )   | $I_{SOURCE} = 200 \ \mu A$                                  | $V_{\text{DRIVE}} - 0.$ | 2   |                  | V    |

| Output Low Voltage (V <sub>OL</sub> )    | I <sub>SINK</sub> = 200 μA                                  |                         |     | 0.4              | V    |

| CONVERSION RATE                          |                                                             |                         |     |                  |      |

| Conversion Time                          | 16 SCLK cycles with SCLK at 20 MHz                          |                         |     | 800              | ns   |

| Throughput Rate                          | ut Rate                                                     |                         |     | 1                | MSPS |

| POWER SUPPLY                             | All at $T_A = -40^{\circ}$ C to $+85^{\circ}$ C             |                         |     |                  |      |

| Vcc                                      |                                                             | 4.75                    | 5   | 5.25             | V    |

| V <sub>DRIVE</sub>                       |                                                             |                         |     | 5.25             | V    |

| V <sub>cc</sub> Quiescent Supply Current | $V_{CC} = 5 V$ , $f_{SCLK} = 50 \text{ kSPS}$               |                         | 7.0 | 9.0              | mA   |

| VDRIVE Quiescent Supply Current          | RIVE Quiescent Supply Current VDRIVE = 5 V, fSCLK = 50 kSPS |                         | 70  | 500              | μA   |

| Power Dissipation                        | $V_{CC} = V_{DRIVE} = 5 V$ , $f_{SCLK} = 50 \text{ kSPS}$   |                         | 40  |                  | mW   |

| TEMPERATURE RANGE                        |                                                             |                         |     |                  |      |

| Specified Performance                    | Tested to max and min specifications                        | -40                     |     | +85              | °C   |

<sup>1</sup> All minimum and maximum specifications are guaranteed. Typical specifications are neither tested nor guaranteed.

<sup>2</sup> Dynamic range is the maximum full-scale measurement range possible, including output swing range, initial offset, sensitivity, offset drift, and sensitivity drift at 5 V <sup>3</sup> Defined as the output change from ambient to maximum temperature, or ambient to minimum temperature.

<sup>4</sup> Frequency at which the response is 3 dB down from dc response. Bandwidth =  $1/(2 \times \pi \times 180 \text{ k}\Omega \times (22 \text{ nF} + C_{OUT}))$ . For  $C_{OUT} = 0$ , bandwidth = 40 Hz. For  $C_{OUT} = 1 \mu F$ , bandwidth = 0.87 Hz.

<sup>5</sup> Self-test response varies with temperature.

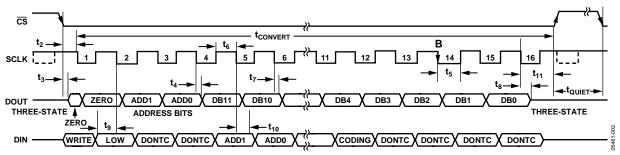

#### TIMING SPECIFICATIONS

$T_A = 25^{\circ}$ C, angular rate = 0°/sec, unless otherwise noted.<sup>1</sup>

| Table 2.                       |                            |            |                                                                                               |

|--------------------------------|----------------------------|------------|-----------------------------------------------------------------------------------------------|

| Parameter                      | $V_{CC} = V_{DRIVE} = 5 V$ | Unit       | Description                                                                                   |

| f <sub>SCLK</sub> <sup>2</sup> | 10                         | kHz min    |                                                                                               |

|                                | 20                         | MHz max    |                                                                                               |

| <b>t</b> convert               | 16 × t <sub>SCLK</sub>     |            |                                                                                               |

|                                | 50                         | ns min     | Minimum quiet time required between $\overline{CS}$ rising edge and start of next conversion. |

| t <sub>2</sub>                 | 10                         | ns min     | CS to SCLK setup time.                                                                        |

| t <sub>3</sub> <sup>3</sup>    | 30                         | ns max     | Delay from $\overline{CS}$ until DOUT three-state disabled.                                   |

| t4 <sup>3</sup>                | 40                         | ns max     | Data access time after SCLK falling edge.                                                     |

| t5                             | $0.4 \times t_{SCLK}$      | ns min     | SCLK low pulse width.                                                                         |

| t <sub>6</sub>                 | $0.4 \times t_{SCLK}$      | ns min     | SCLK high pulse width.                                                                        |

| t7                             | 10                         | ns min     | SCLK to DOUT valid hold time.                                                                 |

| t <sub>8</sub> 4               | 15/35                      | ns min/max | SCLK falling edge to DOUT high impedance.                                                     |

| t9                             | 10                         | ns min     | DIN setup time prior to SCLK falling edge.                                                    |

| t <sub>10</sub>                | 5                          | ns min     | DIN hold time after SCLK falling edge.                                                        |

| <b>t</b> 11                    | 20                         | ns min     | 16 <sup>th</sup> SCLK falling edge to $\overline{CS}$ high.                                   |

<sup>1</sup> Guaranteed by design. All input signals are specified with  $t_R$  and  $t_F = 5$  ns (10% to 90% of  $V_{CC}$ ) and timed from a voltage level of 1.6 V. The 5 V operating range spans from 4.75 V to 5.25 V.

<sup>2</sup> Mark/space ratio for the SCLK input is 40/60 to 60/40.

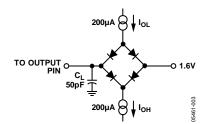

$^3$  Measured with the load circuit in Figure 3 and defined as the time required for the output to cross 0.4 V, or 0.7 × V<sub>DRIVE</sub>.

<sup>4</sup> t<sub>8</sub> is derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit in Figure 3. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, t<sub>8</sub>, quoted in the timing characteristics is the true bus relinquish time of the part and is independent of the bus loading.

Figure 2. Gyroscope Serial Interface Timing Diagram

Figure 3. Load Circuit for Digital Output Timing Specifications

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                  | Rating                            |

|--------------------------------------------|-----------------------------------|

| Acceleration (Any Axis, Unpowered, 0.5 ms) | 2000 g                            |

| Acceleration (Any Axis, Powered, 0.5 ms)   | 2000 g                            |

| V <sub>CC</sub> to COM                     | –0.3 V to +6.0 V                  |

| V <sub>DRIVE</sub> to COM                  | $-0.3V$ to $V_{CC}$ + 0.3 $V$     |

| Analog Input Voltage to COM                | -0.3 V to V <sub>CC</sub> + 0.3 V |

| Digital Input Voltage to COM               | –0.3 V to +7.0 V                  |

| Digital Output Voltage to COM              | $-0.3V$ to $V_{CC}$ + 0.3 $V$     |

| ST1/ST2 Input Voltage to COM               | $-0.3$ V to $V_{CC}$ + 0.3 V      |

| Operating Temperature Range                | –55°C to +125°C                   |

| Storage Temperature Range                  | –65°C to +150°C                   |

Stresses above those listed under the Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Drops onto hard surfaces can cause shocks of greater than 2000 *g* and exceed the absolute maximum rating of the device. Care should be exercised in handling to avoid damage.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

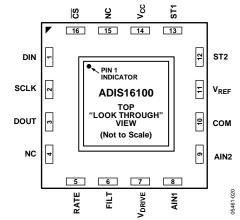

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES

1. NC = NO CONNECT 2. THIS IS NOT AN ACTUAL "TOP VIEW," AS THE PINS ARE NOT VISIBLE FROM THE TOP. THIS IS A LAYOUT VIEW, WHICH REPRESENTS THE PIN CONFIGURATION, IF THE PACKAGE IS LOOKED THROUGH FROM THE TOP. THIS CONFIGURATION IS PROVIDED FOR PCB LAYOUT PURPOSES.

Figure 4. Pin Configuration, Top Look-Through View

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic           | Type <sup>1</sup> | Description                                                                                               |

|---------|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| 1       | DIN                | 1                 | SPI Data Input.                                                                                           |

| 2       | SCLK               | I                 | SPI Serial Clock.                                                                                         |

| 3       | DOUT               | 0                 | SPI Data Output.                                                                                          |

| 4       | NC                 |                   | No Connect.                                                                                               |

| 5       | RATE               | 0                 | Buffered Analog Output. Represents the angular rate signal.                                               |

| 6       | FILT               | I                 | External Capacitor Connection to Control Bandwidth.                                                       |

| 7       | V <sub>DRIVE</sub> | S                 | SPI Power Supply. This can be the receive processing circuit's supply to simplify interfacing.            |

| 8       | AIN1               | I                 | External Analog Input Channel 1. See ADD0 and ADD1 address bits in Table 5.                               |

| 9       | AIN2               | I                 | External Analog Input Channel 2. See ADD0 and ADD1 address bits in Table 5.                               |

| 10      | СОМ                | S                 | Common. Reference point for all circuitry in the ADIS16100.                                               |

| 11      | V <sub>REF</sub>   | 0                 | Precision 2.5 V Reference.                                                                                |

| 12      | ST2                | I                 | Self-Test Input 2.                                                                                        |

| 13      | ST1                | I                 | Self-Test Input 1.                                                                                        |

| 14      | Vcc                | S                 | Analog Power.                                                                                             |

| 15      | NC                 |                   | No Connect.                                                                                               |

| 16      | CS                 | Ι                 | Chip Select. Active low. This input frames the serial data transfer and initiates the conversion process. |

<sup>1</sup> I = input; O = output; S = power supply.

Rev. B | Page 7 of 16

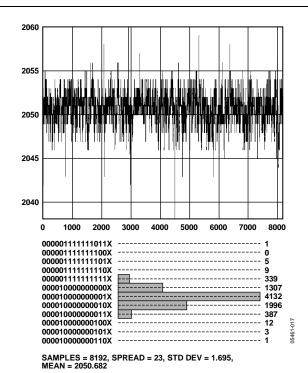

Figure 19. Noise Histogram

### THEORY OF OPERATION

The ADIS16100 operates on the principle of a resonator gyroscope. Two polysilicon sensing structures each contain a dither frame that is electrostatically driven to resonance. This produces the necessary velocity element to produce a Coriolis force while rotating. At two of the outer extremes of each frame, orthogonal to the dither motion, are movable fingers that are placed between fixed pickoff fingers to form a capacitive pickoff structure that senses Coriolis motion. The resulting signal is fed to a series of gain and demodulation stages that produce the electrical rate signal output. The rate signal is then converted to a digital representation of the output on the SPI pins. The dualsensor design rejects external *g* forces and vibration. Fabricating the sensor with the signal conditioning electronics preserves signal integrity in noisy environments.

The electrostatic resonator requires 14 V to 16 V for operation. Because only 5 V is typically available in most applications, a charge pump is included on-chip. After the demodulation stage, there is a single-pole, low-pass filter included on-chip that is used to limit high frequency artifacts before final amplification. The frequency response is dominated by the second low-pass filter, which is set at 40 Hz. For additional bandwidth reduction options, see the Setting Bandwidth section.

#### SUPPLY AND COMMON CONSIDERATIONS

Power supply noise and transient behaviors can influence the accuracy and stability of any sensor-based measurement system. When considering the power supply for the ADIS16100, it is important to understand that the ADIS16100 provides 0.2  $\mu$ F of decoupling capacitance on the V<sub>CC</sub> pin. Depending on the level of noise present in the system power supply, the ADIS16100 may not require any additional decoupling capacitance for this supply. The analog supply, V<sub>CC</sub>, and the digital drive supply, V<sub>DRIVE</sub>, are segmented to allow multiple logic levels to be used in receiving the digital output data. V<sub>DRIVE</sub> is intended for the downstream logic power supply and supports standard 3.3 V and 5 V logic families. The V<sub>DRIVE</sub> supply does not have internal decoupling capacitors.

#### **INCREASING MEASUREMENT RANGE**

The full-scale measurement range of the ADIS16100 is increased by placing an external resistor between the RATE pin and FILT pin, which results in a parallel connection with the internal 180 k $\Omega$ , 1% resistor. For example, a 330 k $\Omega$  external resistor gives ~50% increase in the full-scale range. This is effective for up to a 4× increase in the full-scale range (minimum value of the parallel resistor allowed is 45 k $\Omega$ ). The internal circuitry headroom requirements prevent further increase in the linear full-scale output range. The trade-offs associated with increasing the full-scale range are potential increase in output null drift (as much as 2°/sec over temperature) and introducing initial null bias errors that must be calibrated.

#### **SETTING BANDWIDTH**

An external capacitor can be used in combination with an onchip resistor to create a low-pass filter to limit the bandwidth of the ADIS16100 rate response.

The -3 dB frequency is defined as

$$f_{OUT} = 1/(2 \times \pi \times R_{OUT} \times (C_{OUT} + 0.022 \,\mu\text{F}))$$

where:

$R_{OUT}$  is the internal impedance that was trimmed during manufacturing to 180 k $\Omega \pm 1\%$ .

$C_{\rm OUT}$  is the external capacitance across the RATE and FILT pins.

Any external resistor applied between the RATE pin and the FILT pin results in

$$R_{OUT} = (180 \text{ k}\Omega \times R_{EXT}) / (180 \text{ k}\Omega + R_{EXT})$$

where  $R_{EXT}$  is the external resistor.

With  $C_{OUT} = 0 \ \mu F$ , a default  $-3 \ dB$  frequency response of 40 Hz is obtained based upon an internal 0.022  $\mu F$  capacitor implemented on-chip.

#### **SELF-TEST FUNCTION**

The ADIS16100 includes a self-test feature that actuates each of the sensing structures and associated electronics in the same manner as if subjected to an angular rate. It provides a simple method for exercising the mechanical structure of the sensor, along with the entire signal processing circuit. It is activated by standard logic high levels applied to Input ST1, Input ST2, or both. ST1 causes a change in the digital output equivalent to typically –220 LSB, and ST2 causes an opposite +220 LSB change. The self-test response follows the viscosity temperature dependence of the package atmosphere, approximately 0.25%/°C. Activating both ST1 and ST2 simultaneously is not damaging. Because ST1 and ST2 are not necessarily closely matched, actuating both simultaneously can result in an apparent null bias shift.

#### **Continuous Self-Test**

As an additional failure detection measure, a power-on self-test can be performed. However, some applications warrant a continuous self-test while sensing rate.

#### **RATE SENSITIVE AXIS**

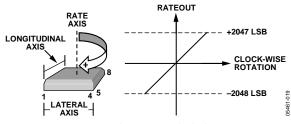

Figure 20. Rate Signal Increases with Clockwise Rotation

### **BASIC OPERATION**

The ADIS16100 is designed for simple integration into industrial system designs, requiring only a 5.0 V power supply and a 4-wire, industry standard serial peripheral interface (SPI). The SPI handles all digital I/O communication in the ADIS16100.

#### **SERIAL PERIPHERAL INTERFACE (SPI)**

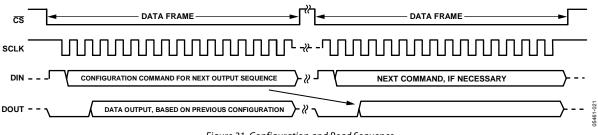

The ADIS16100 SPI port includes four signals: chip select  $(\overline{CS})$ , serial clock (SCLK), data input (DIN), and data output (DOUT). The  $\overline{CS}$  line enables the ADIS16100 SPI port and frames each SPI event. When this signal is high, the DOUT lines are in a high impedance state and the signals on DIN and SCLK have no impact on operation. A complete data frame contains 16 clock cycles. Because the SPI port operates in full duplex mode, it supports simultaneous, 16-bit receive (DIN) and transmit (DOUT) functions within the same data frame.

#### **Control Register**

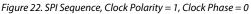

The DIN control register provides controls for two operational settings: the output data source and the coding (twos complement vs. offset binary). Table 5 and Figure 22 provide the proper bit definitions for control register configuration. The DIN sequence starts with a 1 for configuration sequences and a 0 for read sequences. When this bit is 0, the remaining DIN bits do not change the control register and the next sample's output data reflects the existing configuration. Data loads from the DIN pin into the ADIS16100 on the falling edge of SCLK. Once the 16-SCLK sequence is complete, the control register is updated and ready for the next read sequence. If a data frame has less than 16 SCLK cycles, the control register does not update and maintains its previous configuration. The DIN bit definitions in Table 5, which have either 0 or 1 assigned to them, are critical for proper operation.

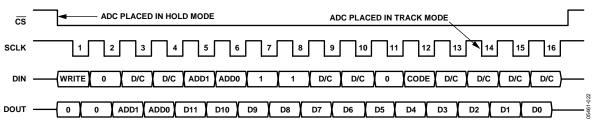

#### ADC Conversion

The chip select  $(\overline{CS})$  and serial clock (SCLK) lines control the on-board analog-to-digital conversion process. When the chip select line goes low, the DOUT line comes out of three-state mode, the track-and-hold goes into hold mode, and the ADC samples the analog input at this point. The track-and-hold returns to track mode on the 14<sup>th</sup> falling edge of the SCLK line. The serial clock drives the internal ADC conversion clock, using its falling edge for control of this process. All 16 SCLK cycles are required for a complete conversion. If a data frame has less than 16 SCLK cycles, the conversion cannot complete and does not update the output data for the next data frame cycle.

#### **Output Data Access**

The DOUT sequence starts with two zeros, one that clocks out after the falling edge of  $\overline{CS}$ , and a second one that clocks out on the first SCLK falling edge. The next 14 bits, ADD0, ADD1 and the 12 data bits, clock out on SCLK falling edges. After the 16<sup>th</sup> falling edge, the DOUT line moves to a three-state mode.

When setting up the system process to receive data from the ADIS16100, use a clock phase setting of 0 and a clock polarity setting of 1. These settings reflect the timing displayed in Figure 22. To maintain proper communication at the maximum specified clock rates, the system processor must be able to support the setup time requirement, listed in Figure 2 and Table 2 ( $t_9$ ).

Figure 21. Configuration and Read Sequence

#### Table 5. DIN Bit Assignments

| Tuble 5. Diff Die Hooignitiento |            |                                     |  |  |  |

|---------------------------------|------------|-------------------------------------|--|--|--|

| Bit No.                         | Mnemonic   | Comment                             |  |  |  |

| 15                              | WRITE      | 1: Write contents on DIN to control |  |  |  |

|                                 |            | register.                           |  |  |  |

|                                 |            | 0: No changes to control register.  |  |  |  |

| 14                              | 0          | Low state for normal operation.     |  |  |  |

| 13, 12                          | D/C        | Don't care.                         |  |  |  |

| 11, 10                          | ADD1, ADD0 | Data source setting.                |  |  |  |

|                                 |            | 00: Gyroscope output.               |  |  |  |

|                                 |            | 01: Temperature output.             |  |  |  |

|                                 |            | 10: Analog input 1.                 |  |  |  |

|                                 |            | 11: Analog input 2.                 |  |  |  |

| 9, 8                            | 1          | High state for normal operation.    |  |  |  |

| 7,6                             | D/C        | Don't care.                         |  |  |  |

| 5                               | 0          | Low state for normal operation.     |  |  |  |

| 4                               | CODE       | Output data format setting.         |  |  |  |

|                                 |            | 0: Twos complement.                 |  |  |  |

|                                 |            | 1: Offset binary.                   |  |  |  |

| 3 to 0                          | D/C        | Don't care.                         |  |  |  |

#### **Output Coding Examples**

#### Table 6. Gyroscope Data Coding, Twos Complement

| Angular Rate (°/sec) | Code  | Bit Pattern                             |

|----------------------|-------|-----------------------------------------|

| 300                  | 1230  | 0000010011001110                        |

|                      |       |                                         |

| 0.4878               | 2     | 0000000000000010                        |

| 0.2439               | 1     | 000000000000000000000000000000000000000 |

| 0                    | 0     | 000000000000000000000000000000000000000 |

| -0.2439              | -1    | 11111111111111111                       |

| -0.4878              | -2    | 11111111111111110                       |

|                      |       |                                         |

| -300                 | -1230 | 0000101100110010                        |

#### Table 7. Gyroscope Data Coding, Offset Binary

| Angular Rate (°/sec) | Code | Bit Pattern      |

|----------------------|------|------------------|

| Aliguial Rate (7sec) | Code | BILFALLEITI      |

| 300                  | 3278 | 0000110011001110 |

|                      |      |                  |

| •••                  | •••  | •••              |

| 0.4878               | 2050 | 000010000000010  |

| 0.2439               | 2049 | 0000100000000001 |

| 0                    | 2048 | 000010000000000  |

| -0.2439              | 2047 | 0000111111111111 |

| -0.4878              | 2046 | 0000111111111110 |

|                      |      |                  |

| -300                 | 818  | 0000001100110010 |

#### Table 8. Temperature Data Coding, Twos Complement

| Temperature (°C) | Code | Bit Pattern      |

|------------------|------|------------------|

| 85               | 585  | 0001001001001001 |

|                  |      |                  |

| 25 + 0.2906      | 2    | 000100000000010  |

| 25 + 0.1453      | 1    | 0001000000000001 |

| 25               | 0    | 000100000000000  |

| 25 – 0.1453      | -1   | 0001111111111111 |

| 25 – 0.2906      | -2   | 000111111111110  |

|                  |      |                  |

| -40              | -447 | 0001111001000001 |

#### Table 9. Temperature Data Coding, Offset Binary

| Temperature (°C) | Code | Bit Pattern      |

|------------------|------|------------------|

| 85               | 2633 | 0001101001001001 |

|                  |      |                  |

| 25 + 0.2906      | 2050 | 0001100000000010 |

| 25 + 0.1453      | 2049 | 0001100000000001 |

| 25               | 2048 | 0001100000000000 |

| 25 – 0.1453      | 2047 | 0001111111111111 |

| 25 – 0.2906      | 2046 | 0001111111111110 |

|                  |      |                  |

| -40              | 1601 | 0001011001000001 |

#### Table 10. ADC Data Coding, Twos Complement

| Input Level (V) | Code <sup>1</sup> | Bit Pattern      |

|-----------------|-------------------|------------------|

| 2               | 1638              | 0010011001100110 |

|                 |                   |                  |

| 0.002442        | 2                 | 001000000000010  |

| 0.001221        | 1                 | 001000000000001  |

| 0               | 0                 | 00100000000000   |

| -0.001221       | -1                | 001011111111111  |

| -0.002442       | -2                | 001011111111110  |

|                 |                   |                  |

| -2              | -1638             | 0010100110011010 |

<sup>1</sup> Code for AIN1 used in 3<sup>rd</sup> and 4<sup>th</sup> bits (11 for AIN2).

#### Table 11. ADC Data Coding, Offset Binary

| Input Level (V) | Code <sup>1</sup> | Bit Pattern      |

|-----------------|-------------------|------------------|

| 2               | 3686              | 0010011001100110 |

|                 |                   |                  |

| 0.002442        | 2050              | 001010000000010  |

| 0.001221        | 2049              | 001010000000001  |

| 0               | 2048              | 001010000000000  |

| -0.001221       | 2047              | 001011111111111  |

| -0.002442       | 2046              | 001011111111110  |

|                 |                   |                  |

| -2              | 410               | 0010000110011010 |

<sup>1</sup> Code for AIN1 used in 3<sup>rd</sup> and 4<sup>th</sup> bits (11 for AIN2).

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model         | Temperature Range | Package Description                       | Package Option |

|---------------|-------------------|-------------------------------------------|----------------|

| ADIS16100ACC  | -40°C to +85°C    | 16-Terminal Stacked Land Grid Array (LGA) | CC-16-1        |

| ADIS16100/PCB |                   | Evaluation Board                          |                |

### NOTES

### NOTES

www.analog.com

©2006–2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05461-0-6/07(B)

Rev. B | Page 16 of 16